摩爾定律的延伸受到物理極限、巨額資金投入等多重壓力,迫切需要别開(kāi)蹊徑延續工藝進(jìn)步。而通過(guò)先進(jìn)封裝集成(chéng)技術,可以更輕松地實現高密度集成(chéng)、體積微型化和更低的成(chéng)本。封裝行業將(jiāng)在集成(chéng)電路整體系統整合中扮演更重要的角色,也將(jiāng)對(duì)産業的格局形成(chéng)更多影響。随着先進(jìn)封裝的推進(jìn),集成(chéng)電路産業將(jiāng)展現出一些新的發(fā)展趨勢,有先進(jìn)封裝的集成(chéng)電路産業樣貎將(jiāng)會有所不同。

先進(jìn)封裝增速遠超傳統封裝

當前社會正處于新技術與新應用全面(miàn)爆發(fā)的背景下,移動設備、大數據、人工智能(néng)、5G通信、高性能(néng)計算、物聯網、智能(néng)汽車、智能(néng)工業等快速發(fā)展。這(zhè)些技術與應用必將(jiāng)對(duì)底層芯片技術産生新的需求。據麥姆斯咨詢的介紹,支持這(zhè)些新興大趨勢的電子硬件需要高計算能(néng)力、高速度、更多帶寬、低延遲、低功耗、更多功能(néng)、更多内存、系統級集成(chéng)、更精密的傳感器,以及最重要的低成(chéng)本。這(zhè)些新興趨勢將(jiāng)爲各種(zhǒng)封裝平台創造商機,而先進(jìn)封裝技術是滿足各種(zhǒng)性能(néng)要求和複雜異構集成(chéng)需求的理想選擇。

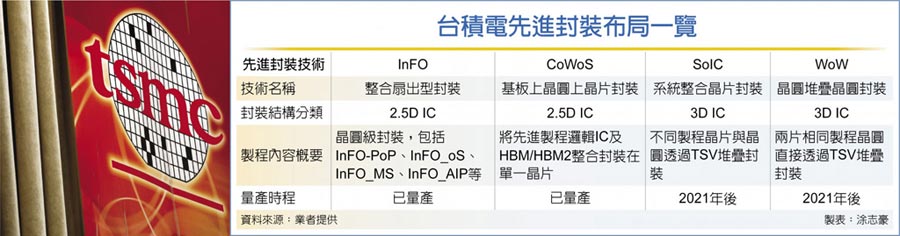

目前來看,扇出型封裝(FOWLP/)、系統級封裝(SiP)、3D封裝是最受關注的三種(zhǒng)先進(jìn)封裝技術。扇出型封裝是晶圓級封裝中的一種(zhǒng),相對(duì)于傳統封裝具有不需要引線框、基闆等介質的特點,因此可以實現更輕薄短小的封裝。根據IC Insight預計,在未來數年之内,利用扇出型封裝技術生産的芯片,每年將(jiāng)以32%的增長(cháng)率持續擴大,2023年扇出型封裝市場規模將(jiāng)超過(guò)55億美元。

系統級封裝可以將(jiāng)一個或多個IC芯片及被動元件整合在一個模塊中,從而實現具有完整功能(néng)的電路集成(chéng),它也可以降低成(chéng)本,縮短上市時間,同時克服了SoC中諸如工藝兼容、信号混合、噪聲幹擾、電磁幹擾等難題。

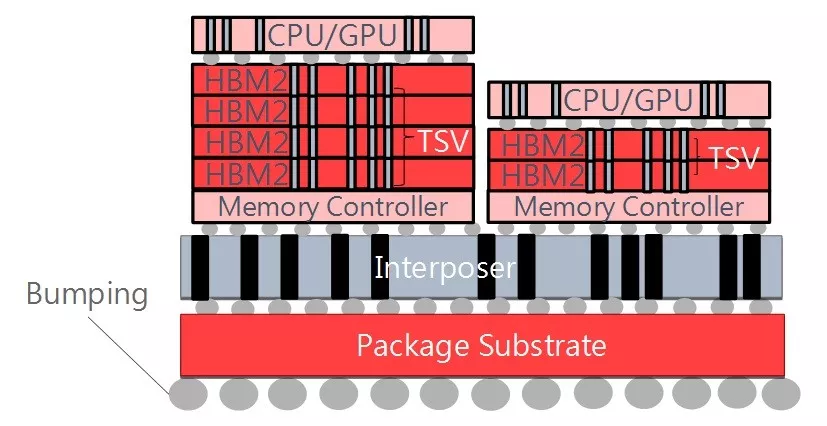

3D封裝通過(guò)晶圓級互連技術實現芯片間的高密度封裝,可以有效滿足高功能(néng)芯片超輕、超薄、高性能(néng)、低功耗及低成(chéng)本的需求,被大多半導體廠商認爲是最具有潛力的封裝方法。

總之,在市場需求的帶動下,越來越多先進(jìn)封裝技術被開(kāi)發(fā)出來,先進(jìn)封裝的市場占比將(jiāng)會進(jìn)一步擴大。統計數據顯示,從2017年到2023年,整個半導體封裝市場的營收將(jiāng)以5.2%的年複合增長(cháng)率增長(cháng),而先進(jìn)封裝市場將(jiāng)以7%的年複合增長(cháng)率增長(cháng),市場規模到2023年將(jiāng)增長(cháng)至390億美元,傳統封裝市場的複合年增長(cháng)率則低于3.3%。

展現三大發(fā)展趨勢

随着先進(jìn)封裝技術的發(fā)展以及市場規模的擴大,其對(duì)于整個集成(chéng)電路産業結構將(jiāng)産生越來越大的影響。首先是中段工藝的出現并逐漸形成(chéng)規模。随着傳統封裝技術向(xiàng)先進(jìn)封裝過(guò)渡,有别于傳統封裝技術的凸塊(Bumping)、再布線(RDL)、矽通孔(TSV)等中段工藝被開(kāi)發(fā)出來,并且開(kāi)始發(fā)揮重要作用。中芯長(cháng)電半導體首席執行官崔東表示,僅靠縮小線寬的辦法已經(jīng)無法同時滿足性能(néng)、功耗、面(miàn)積,以及信号傳輸速度等多方面(miàn)的要求,因此半導體企業開(kāi)始把注意力放在系統集成(chéng)層面(miàn)來尋找解決方案,也就是通過(guò)先進(jìn)的矽片級封裝技術,把不同工藝技術代的裸芯封裝在一個矽片級的系統裡(lǐ),兼顧性能(néng)、功耗和傳輸速度的要求。這(zhè)就産生了在矽片級進(jìn)行芯片之間互聯的需要,進(jìn)而産生了凸塊、再布線、矽通孔等中段工藝。而中段矽片加工的出現,也打破了前後(hòu)段芯片加工的傳統分工方式。

其次,制造與封裝將(jiāng)形成(chéng)新的競合關系。由于先進(jìn)封裝帶來的中段工藝,封測業和晶圓制造業有了更緊密的聯系,在帶來發(fā)展機遇的同時,也面(miàn)臨着新的挑戰。中段封裝的崛起(qǐ)必然擠壓晶圓制造或者封裝測試業的份額。有迹象表明,部分晶圓廠已加大在中段封裝工藝上的布局。晶圓廠有着技術和資本的領先優勢,將(jiāng)對(duì)封測廠形成(chéng)較大的競争壓力。傳統封測廠較晶圓制造業相比屬于輕資産,引入中段工藝後(hòu),設備資産比重較傳統封裝大大增加,封測業的先進(jìn)技術研發(fā)和擴産將(jiāng)面(miàn)臨較大的資金壓力。

最後(hòu),推動集成(chéng)電路整體實力的提升。後(hòu)摩爾時代的集成(chéng)電路産業更強調産業鏈的緊密合作,強化産業鏈上下遊之間的内在聯系,要求各個環節不再是割裂地單獨進(jìn)行生産加工,而是要求從系統設計、産品設計、前段工藝技術和封測各個環節開(kāi)展更加緊密的合作。企業對(duì)于先進(jìn)封裝業務的競争,最終還(hái)需表現爲産業鏈之間綜合實力的競争。

中國(guó)應加快虛拟IDM生态鏈建設

近幾年中國(guó)集成(chéng)電路封測産業實現了高速發(fā)展,有了長(cháng)足的進(jìn)步,然而國(guó)内集成(chéng)電路封測産業鏈整體技術水平不高也是不争的事(shì)實。半導體專家莫大康認爲,中國(guó)現在非常重視集成(chéng)電路産業,推動先進(jìn)封裝業的發(fā)展就是非常必要的了。中國(guó)的封裝測試是集成(chéng)電路三業(設計、制造、封測)中起(qǐ)步最早的,與國(guó)際水平差距也比較小,因此完全有能(néng)力發(fā)展起(qǐ)來。

華進(jìn)半導體總經(jīng)理曹立強在近日的演講中再次提出,推動國(guó)内“EDA軟件—芯片設計—芯片制造—芯片封測—整機應用”集成(chéng)電路産業鏈虛拟IDM生态鏈的建設,以市場需求牽引我國(guó)集成(chéng)電路封測産業快速發(fā)展。集成(chéng)電路的競争最終會表現爲産業鏈之間綜合實力的競争,先進(jìn)封裝的發(fā)展需要從工藝、設備和材料等方面(miàn)的協同。

在新的技術趨勢和競争環境下,集成(chéng)電路産業越來越表現爲産業鏈整體實力的競争。過(guò)去幾年,國(guó)際半導體制造公司紛紛加大力度向(xiàng)先進(jìn)工藝挺進(jìn),在持續大規模資本投入擴建産能(néng)的帶動下,一些半導體制造大廠同樣具備了完整的先進(jìn)封裝制造能(néng)力。

應對(duì)這(zhè)樣的産業形勢,曹立強指出,重點在于突破一些關鍵性技術,如高密度封裝關鍵工藝、三維封裝關鍵技術、多功能(néng)芯片疊層集成(chéng)關鍵技術、系統級封裝關鍵技術等。建設立足應用、重在轉化、多功能(néng)、高起(qǐ)點的虛拟IDM産業鏈,解決集成(chéng)電路産業領域的關鍵技術,突破技術瓶頸。