近期電子科技大學(xué)張波教授提出“特色工藝將(jiāng)成(chéng)爲中國(guó)半導體業的機遇”,由于有獨特的見解,已引發(fā)業界的贊許。

特色工藝這(zhè)個詞有些“新”,但是經(jīng)張波教授的解釋,它原是摩爾定律的三個方向(xiàng)之一,英語叫(jiào)“More Than Moore”,之前的譯名爲“超越摩尓定律”。

張波教授把“特色工藝”稱爲“非尺寸依賴”, 是指器件價值或者性能(néng)的提升,不完全靠尺寸縮小,而是通過(guò)功能(néng)的增加。

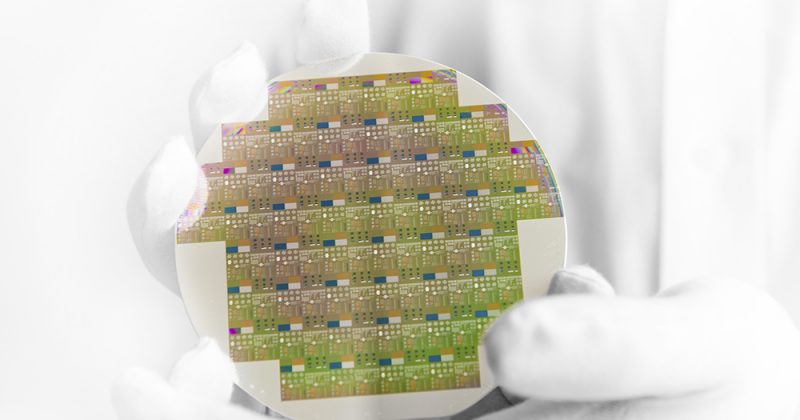

實際上定律延續50多年來,半導體業的驅動力有兩(liǎng)個,一個是尺寸縮小,另一個是矽片直徑增大,顯然尺寸縮小起(qǐ)主要作用。

由于定律有自身的局限性,在那個時代它隻能(néng)預測到晶體管的密度要增加,成(chéng)本可下降,實際上它無法揭示随之而來的功耗增大及晶體管的性能(néng)提高等。所以近期指出定律的另一個方向(xiàng),”非尺寸依賴”具有指導意義。

爲什麼(me)特色工藝成(chéng)香饽饽

全球半導體業在2000年時銷售額達2000億美元,至2013年,經(jīng)過(guò)13年時間達到3000億美元,然而僅用了4年時間,至2017年時己上升到4000億美元,而2018年達到4700億美元,非常可能(néng)在2020年時達到5000億美元。它反映全球電子産品市場中矽含量的急速提升及價值鏈的體現。

但是從另一方面(miàn)觀察,由于定律不可避免的趨向(xiàng)物理極限,IC設計成(chéng)本的急速飙升,全球能(néng)夠繼續追蹤尺寸縮小的廠商數量越來越少,導緻依賴工藝尺寸縮小的推動力減弱。所以半導體業界試圖開(kāi)辟另一個戰場,所謂特色工藝其理在其中。

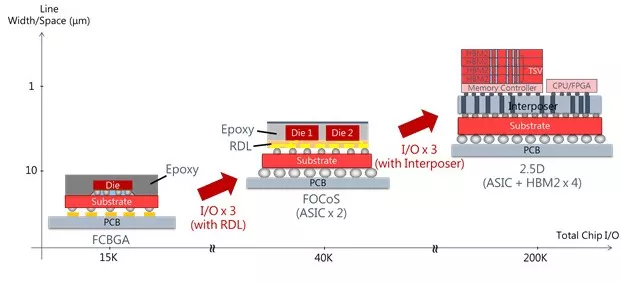

依業界的觀點,特色工藝主要指模拟、RF、功率及MEMS,以及近期非常火熱的2.5D、3D的堆疊封裝等。在未來20年中它非常可能(néng)成(chéng)爲主要推動力之一。

按現在的認識,特色工藝可能(néng)集中于8英寸矽片,及少部分的12英寸矽片中,從工藝尺寸覆蓋可能(néng)在28nm以上。顯然這(zhè)個分界線逐步在改變,在2000年時12英寸矽片剛興起(qǐ)時,這(zhè)個分界線是90nm。如今8英寸矽片逐步升級也己擴展到65nm。這(zhè)一切取決于經(jīng)濟因素,因爲升級8英寸設備要投資,以及90nm以下的光刻機需要重新購買,增加了成(chéng)本。

如果采用8英寸矽片設備作特色工藝,有它的獨特優勢:1),設備的折舊期已過(guò),節省成(chéng)本;2),250nm-130nm工藝相對(duì)成(chéng)熟穩定;3),設備的軟件升級較少受原廠控制等。

張波教授總結特色工藝具有市場分散,品種(zhǒng)衆多、與應用關系強,且無壟斷企業等特點。

但是仔細羅列全球摸拟,RF,功率及MEMS等全球前十位廠商中,發(fā)現排在前列的都(dōu)是曆史悠久的資深老廠,如歐洲的NXP、Infineon及STMicron及日本的Sony、東芝、三菱、富士通、瑞薩、及美國(guó)的TI、Microsemi、及ON Semi等。其中許多廠商至今仍堅守8英寸,甚至6英寸矽片,但是有舉足輕重的地位。

據SEMI 2015年數據,2016年全球8英寸矽片的市場份額,模拟占11%,分立器件14%,邏輯加微處理器21%,存儲器占3%,代工占47%及MEMS加其它占4%。

另據SEMI 2016年數據,2017年全球晶圓産能(néng)爲每月1790萬片(8inch計),其中8英寸産能(néng)爲月産520萬片,約占不到1/3,其中前十大8英寸廠的産能(néng)占總産能(néng)的54%。

特色工藝在中國(guó)

據廈門半導體投資集團總經(jīng)理王彙聯的數據,2018年中國(guó)在建及規劃Fab産線總共33條,包括21條12英寸線、11條8英寸線,其中特色工藝線16條、邏輯産線9條、存儲産線8條。SEMI數據顯示中國(guó)晶圓産能(néng)2019年占到全球16%,到2020年將(jiāng)增至20%。

其中的趨勢是中芯國(guó)際,代工業的領頭羊,除了在國(guó)家資金等支持下,開(kāi)發(fā)14nm及以下邏輯制程工藝之外,積極擴充它的8英寸産能(néng),包括天津,深圳,甯波,紹興等地,而原本生存得很滋潤的華虹,華潤微電子,士蘭等,卻由8英寸延伸至12英寸,目的都(dōu)是爲了實現産品差異化,跨入特色工藝中。

實際上企業的決策才是最真實的反映,它們的感覺十分靈敏及深刻。那麼(me)多條特色工藝生産線的興建,至少反映現階段它可能(néng)适合于中國(guó)半導體業發(fā)展的需要。

因爲從産業利益出發(fā),現階段由中芯國(guó)際,華力微積極跟蹤14nm及以下邏輯制程,以及由長(cháng)江存儲做3D NAND閃存,合肥長(cháng)鑫做19nmDRAM等都(dōu)是很有必要,首先要解決“0”到“1”的突破問題,具備能(néng)力之後(hòu)才逐步擴充産能(néng)。顯然這(zhè)段路十分崎岖,投資巨大及周期長(cháng),技術難度高,未來産品市場的競争力將(jiāng)經(jīng)受考驗。

而絕大部分的中國(guó)半導體企業,它們首要任務是求生存,能(néng)實現盈利,所以讓它們去追蹤定律,或者嘗試存儲器的IDM模式量産是不客觀的。所以它們紛紛轉向(xiàng)選擇特色工藝可能(néng)是必由之路。

分析中國(guó)半導體業在代工業中8英寸制程與全球的先進(jìn)水平接近,有一定優勢,但是在非邏輯制程中,如模拟、高壓、MEMS、包括IDM模式的産品等方面(miàn)可能(néng)差距較大。

另據張波教授的資料,采用特色工藝可能(néng)有助于提高國(guó)産化率。因爲中國(guó)進(jìn)口集成(chéng)電路的均價隻有7毛五,不足一美元。其中進(jìn)口了大量每塊價值達數百美元的高端CPU,同時也大量進(jìn)口了不需要先進(jìn)工藝的分立器件、電源管理IC、微控制器等。因此釆用特色工藝,國(guó)産替代的空間非常巨大。

顯然在市場競争中,對(duì)于中國(guó)半導體業發(fā)展不可能(néng)有一條“捷徑”,做特色工藝是機遇與風險同在。因爲對(duì)手都(dōu)十分強大,經(jīng)驗豐富,而我們是“追趕者”,從先天性方面(miàn)不存在優勢,僅僅是由于市場機會多,産品分散,與應用結合強,而中國(guó)擁有全球最大的市場,具這(zhè)樣的優勢地位有可能(néng)讓我們從中分得一杯羹。

企業成(chéng)功的要素取決于市場空間,技術能(néng)力及時機,關鍵要有一位強有力的CEO。

近期貿易戰對(duì)于中國(guó)半導體業發(fā)展的影響不可小視,一個是電子産業鏈有部分外移出中國(guó),另一個是美國(guó)的封鎖持續加緊等,導緻中國(guó)半導體業要維持年均增長(cháng)率達20%可能(néng)有一定難度。不過(guò)事(shì)物有它的“兩(liǎng)重性”,有時“壞事(shì)”也可能(néng)變成(chéng)“好(hǎo)事(shì)”,如貿易戰下促使部分人才加速回流,以及在外壓力下能(néng)激發(fā)鬥志,更加團結,有可能(néng)取得更大的成(chéng)績。