爲求低功耗、高能(néng)效及高性價比之元件,市場逐漸開(kāi)發(fā)出FD-SOI(完全空乏型矽絕緣層金氧半晶體管)結構;而FD-SOI構造主要以SOI晶圓爲核心,透過(guò)傳統Si芯片制程方式,進(jìn)而以水平式晶體管架構,取代線寬較大(16~12nm)之FinFET元件。

進(jìn)一步分析FD-SOI市占情形,在各廠商相繼投入開(kāi)發(fā)資源下,2018年整體元件市場規模達160億美元,預估2019年整體市場可望達到270億美元(年增68.6%),後(hòu)續成(chéng)長(cháng)态勢也將(jiāng)逐年上揚。

技術的發(fā)展演進(jìn),FD-SOI實現低功耗、高性價比之元件架構

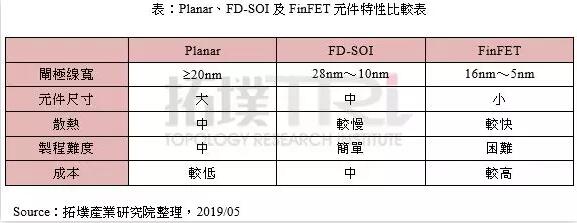

由于半導體發(fā)展趨勢,使得相同面(miàn)積下試圖填入更多晶體管的想法逐漸受到重視,因此衍生出微縮整體尺寸的構想,而閘極(Gate)尺寸將(jiāng)是微縮重點。以傳統Planar元件發(fā)展來看,其閘極線寬已微縮至極限,因而需改變元件結構才能(néng)因應此要求,而立體構造的FinFET(鳍式場效晶體管)元件就在此時被開(kāi)發(fā)出來。

FinFET名稱主要由于元件結構以立體方式呈現,且其閘極構造如同魚鳍一般,豎立于源極(Source)與汲極(Drain)間,作爲控制元件的開(kāi)關。在這(zhè)樣新穎結構下,雖可符合微縮尺寸之需求,但最大問題仍是閘極線寬必須在16nm以下(如12nm、10nm),才能(néng)有效控制從源極到汲極間的電流開(kāi)關。

依現行元件發(fā)展情形,盡管已從傳統的Planar元件推升至FinFET結構,閘極線寬仍存在一段難以使用上的尺寸區,還(hái)需有其他元件技術加以補足,而FD-SOI元件結構剛好(hǎo)補上此缺口,實現低功耗、高性價比、制造周期短之元件架構。

對(duì)于現行技術發(fā)展情形,依照所需元件尺寸及功能(néng)的不同,可區分爲兩(liǎng)大陣營:

精進(jìn)于微縮閘極線寬之FinFET制程技術開(kāi)發(fā)(如台積電、Samsung等),試圖增加晶體管數量,提升整體元件工作效率;

投入FD-SOI制程技術,嘗試開(kāi)發(fā)出低功耗、高性價比之功能(néng)性元件。盡管兩(liǎng)者之曆史脈絡有所不同、技術上各有千秋,但就元件技術發(fā)展趨勢評估,兩(liǎng)者技術仍將(jiāng)持續發(fā)展及并存。

各家大廠投入FD-SOI元件開(kāi)發(fā),看好(hǎo)後(hòu)續市場發(fā)展

FD-SOI元件技術主要源于一種(zhǒng)水平式晶體管結構,透過(guò)SOI晶圓(Si/SiO2(Buried Oxide)/Si Substrate結構)方式,將(jiāng)最上層Si層借由制程、設計以滿足所需功能(néng),并作爲元件導通層之用;而中間SiO2層,憑借于高阻值之材料特性,隔絕晶體管間不必要的寄生電容,提高元件工作效率,因此在這(zhè)樣的制程條件下,FD-SOI可透過(guò)傳統Si芯片的機台進(jìn)行加工,降低開(kāi)發(fā)所需的設備成(chéng)本。

依現行終端産品應用,FD-SOI元件技術將(jiāng)可應用于物聯網IoT、車用元件與MEMS(微機電)元件等領域,目前已有Samsung、GlobalFoundries、STM等大廠相繼投入制程開(kāi)發(fā)上。

雖然這(zhè)些産品大多可由28nm制程條件下進(jìn)行量産,但随着技術進(jìn)步,憑借于閘極線寬逐漸微縮的趨勢帶動下,將(jiāng)驅使制程條件朝向(xiàng)22nm、12nm目标邁進(jìn),甚至進(jìn)一步跨入10nm制程,從而在相同面(miàn)積下産生更多元件,大幅提升整體元件效率。

觀察采用FD-SOI元件的發(fā)展現況,從2017年開(kāi)始,STM已收到Mobileye訂單需求,并運用28nm制程制造ADAS芯片;NXP也于2017年起(qǐ),積極投入i.MX處理器系列的開(kāi)發(fā),并選擇Samsung FD-SOI之28nm制程技術爲合作夥伴。

另外,GlobalFoundries于2018年取得新創公司Arbe Robotics訂單,其FD-SOI元件將(jiāng)使用先進(jìn)的22nm制程技術,目标打造車用雷達芯片。由此可見,各家廠商在車用芯片領域,使用FD-SOI技術已成(chéng)爲一股風潮,後(hòu)續仍看好(hǎo)該技術的市場發(fā)展。