随着大數據、人工智能(néng)、機器學(xué)習、邊緣計算等應用領域快速發(fā)展,FPGA市場規模在不斷顯著增長(cháng)的同時,亦面(miàn)臨着市場對(duì)現場可編程邏輯陣列(FPGA)在性能(néng)等方面(miàn)提出更高的要求,FPGA企業亦不斷推陳出新以應對(duì)新挑戰。

5月21日,FPGA芯片及IP企業Achronix正式發(fā)布其全新FPGA系列産品——Speedster7t,以滿足人工智能(néng)/機器學(xué)習(AI/ML)和高帶寬數據加速應用日益增長(cháng)的需求,Achronix公司總裁兼首席執行官Robert Blake、亞太區總經(jīng)理羅炜亮等亦現身深圳介紹其新産品。

Achronix公司總裁兼首席執行官Robert Blake

全新“FPGA+”——Speedster7t

資料顯示,Achronix成(chéng)立于2004年,總部位于美國(guó),是一家提供FPGA解決方案和支持性設計工具的企業,不僅提供獨立FPGA芯片,還(hái)提供Speedcore嵌入式FPGA(eFPGA)IP。

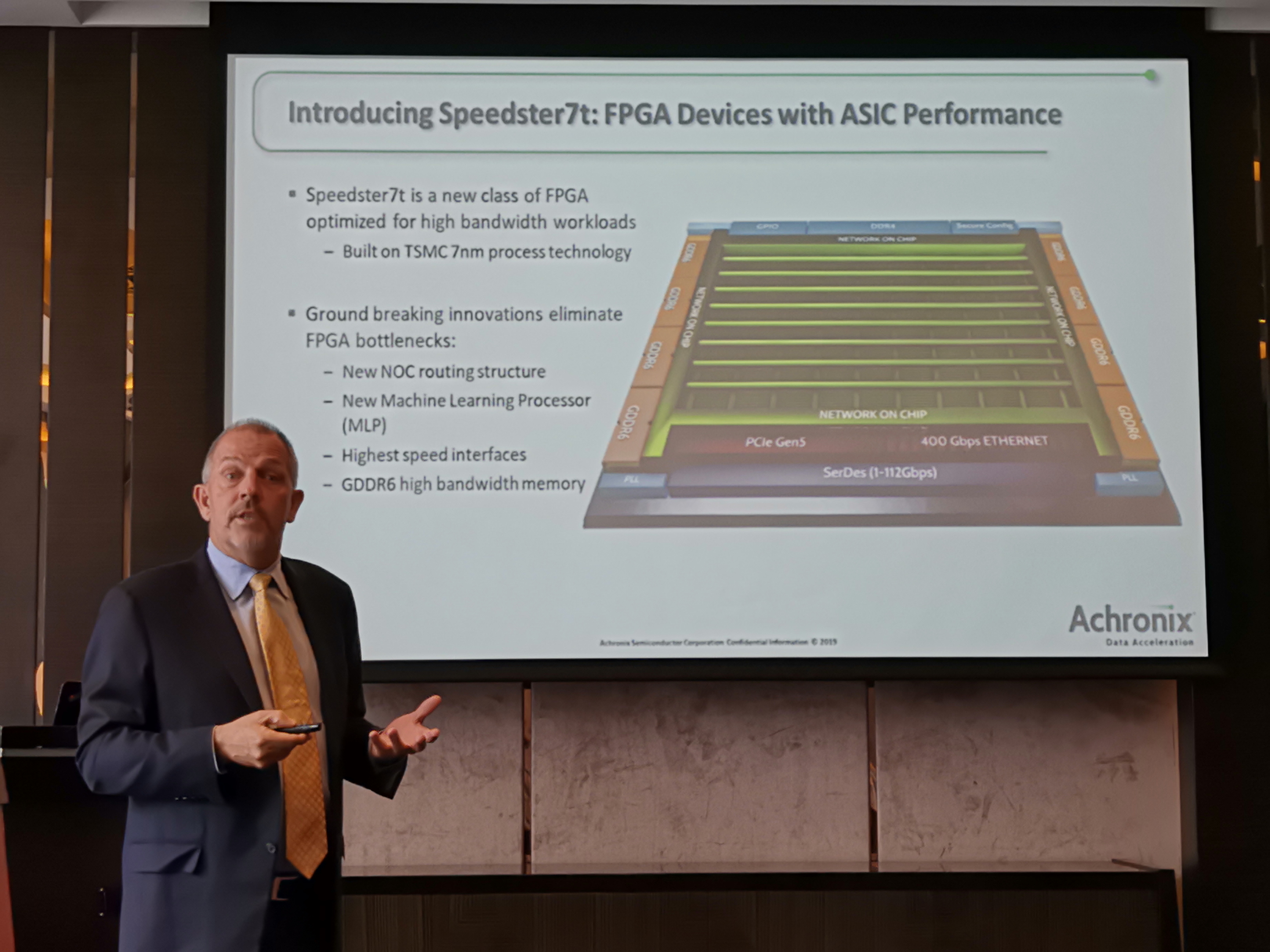

發(fā)布會上,Robert Blake介紹稱,Achronix的Speedster7t FPGA基于一個全新的架構,兼備FPGA的靈活性與ASIC的性能(néng),顯著優于傳統的FPGA解決方案,因此Achronix亦將(jiāng)這(zhè)一全新的芯片品類稱之爲“FPGA+”。

Speedster7t主要面(miàn)向(xiàng)人工智能(néng)/機器學(xué)習(AI/ML)和高帶寬數據加速應用領域,并針對(duì)這(zhè)些領域進(jìn)行了優化。

Robert Blake指出,随着AI/ML等應用市場的日益發(fā)展,AI算法不斷演進(jìn)、數值精度選擇更加多樣,高帶寬數據加速對(duì)架構提出了具備高效計算力、高效大帶寬的數據運送能(néng)力以及高效豐富的存儲緩存能(néng)力等要求,需要提供一個最高能(néng)效比的廣适應平台,Speedster7t則可滿足。

Achronix Speedster7t FPGA基于台積電的7nm FinFET工藝,高帶寬GDDR6接口,400G以太網和PCI Express Gen5端口,所有單元都(dōu)相互連接以提供AISC級帶寬,并保留FPGA的完全可編程性。據Robert Blake介紹,Speedster7t擁有一個全新二維片上網絡(2D NoC)和一個高密度全新機器學(xué)習處理器(MLP)模塊陣列。

MLP高度優化計算性能(néng)

在Robert Blake看來,全新的機器學(xué)習處理器(MLP)是Speedster7t最爲核心并區别于他FPGA産品的地方。

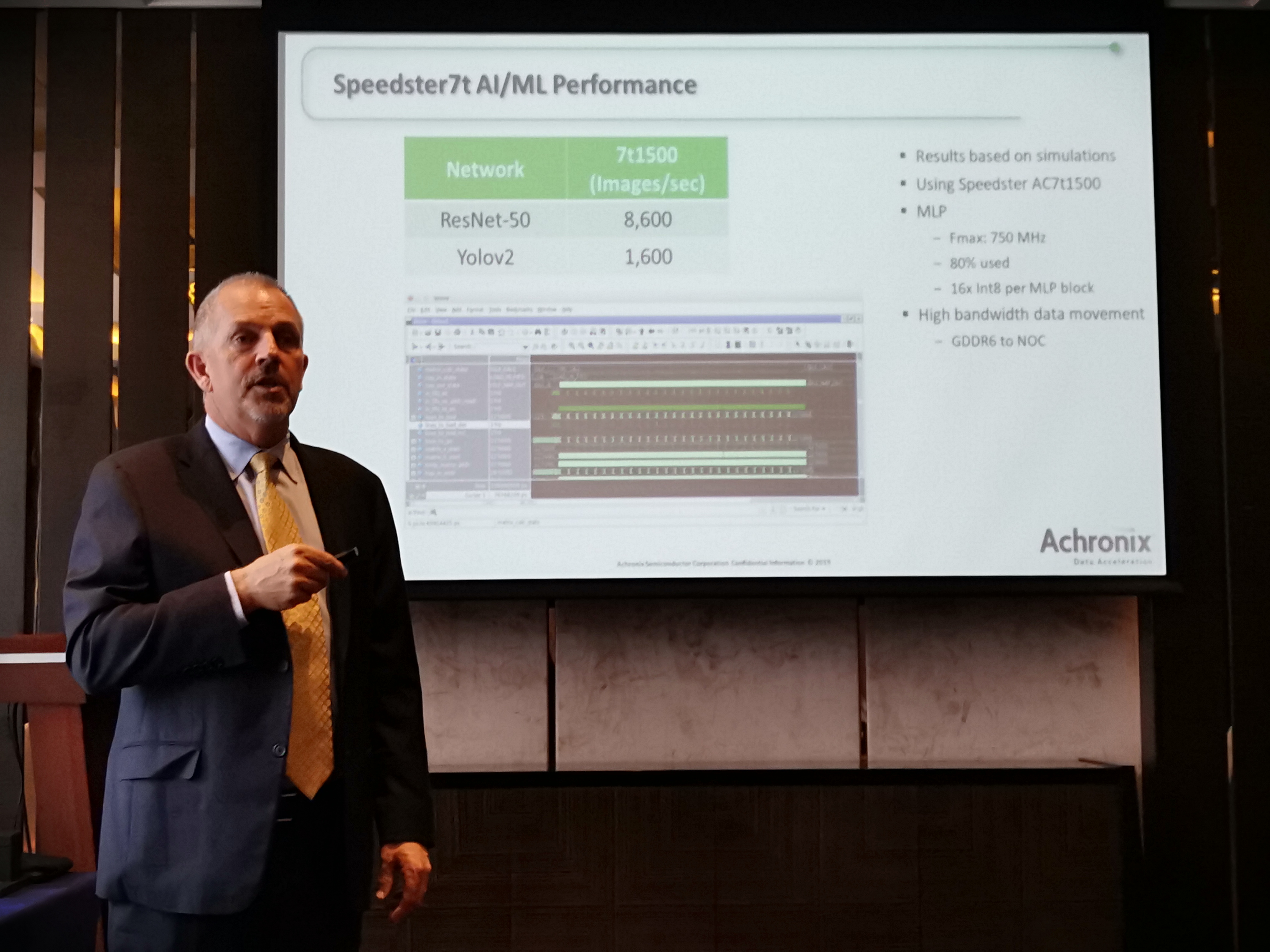

據其介紹,Speedster7t的MLP是高度可配置的計算密集型的單元模塊,具有32個乘法器/累加器(MAC),支持4~24位的整數格式和各種(zhǒng)浮點模式,包括對(duì)Tensorflow的16位格式的本機支持以及高效的塊浮點格式,可顯着提高性能(néng)。

MLP與嵌入式存儲器模塊緊密相鄰,通過(guò)消除傳統設計中與FPGA布線相關的延遲,确保機器學(xué)習算法能(néng)夠以750 MHz的最高性能(néng)運行。這(zhè)種(zhǒng)高密度計算和高性能(néng)數據傳輸的結合使得處理器結構能(néng)夠提供基于FPGA的最高可用于計算能(néng)力以每秒萬億次運算數量爲單位(TOps,tera-operations)。

Robert Blake指出,随着AI/ML的算法不斷更新變化,傳統FPGA采用的DSP架構已不适合用來進(jìn)行AI/ML的運算,存在效率低、性能(néng)受限等現象,Speedster7t全新的MLP架構可實現速度更快、功耗更低、功率更高。

NOC實現高效數據移動

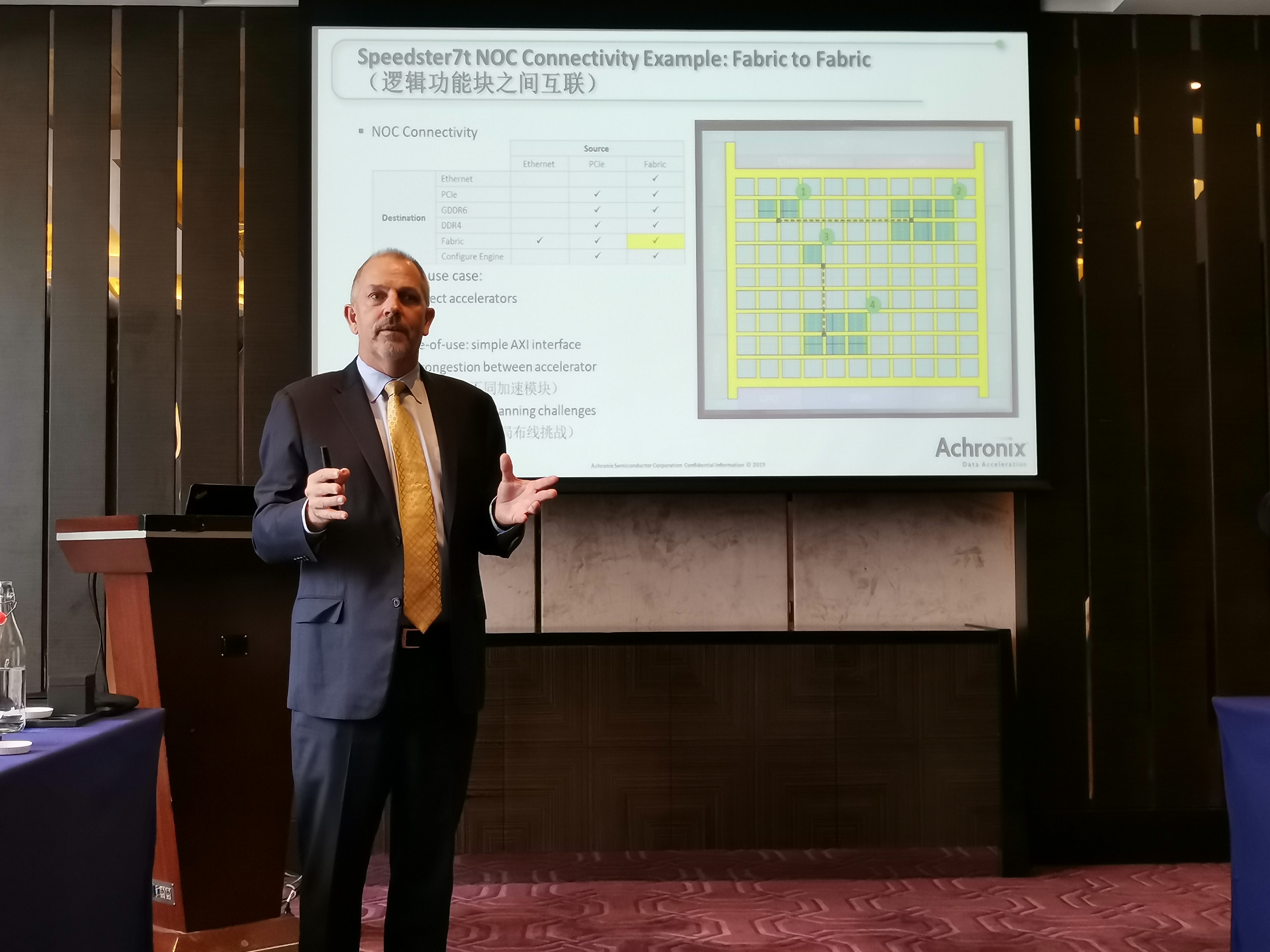

Speedster7t另一個創新性在于其包含一個高帶寬二維片上網絡(NOC),以實現高帶寬加速應用所需的更快數據傳輸速率,設計更簡單、成(chéng)本和功耗更低。

Robert Blake介紹稱,Speedster7t NOC縱橫跨越FPGA邏輯陣列,連接所有FPGA的高速數據和存儲器接口,作用類似于在FPGA可編程邏輯結構上運行的高速公路網絡,可實現高效的數據移動。在他看來,Speedster7t NOC相較于其他企業的同類産品在速度上可能(néng)要快10倍。

Speedster7t NOC支持片上處理引擎間所需的高帶寬通信,其中每一行或每一列都(dōu)可作爲兩(liǎng)個256位實現,單向(xiàng)的、行業标準的AXI通道(dào),工作頻率爲2Ghz,同時可爲每個方向(xiàng)提供512Gbps的數據流量。

Speedster NOC極大簡化了高速數據移動,确保數據流可輕松定向(xiàng)到整個FPGA結構中的任何自定義處理引擎,不需使用任何FPGA内部資源。NOC還(hái)消除了傳統FPGA使用可編程路由和邏輯查找表資源在整個FPGA中移動數據流中出現的擁塞和性能(néng)瓶頸,不僅可提高總帶寬容量,還(hái)能(néng)在降低功耗的同時提高有效LUT容量。

高帶寬、高防護

Robert Blake表示,除了MLP、NOC兩(liǎng)大創新外,Speedster7t FPGA在帶寬、安全防護等方面(miàn)也表現出色。

據其介紹,Speedster7t FPGA是當前唯一支持GDDR6存儲器的FPGA,GDDR6是目前具有最高帶寬的外部存儲器件,每個GDDR6存儲控制器能(néng)支持512Gbps的帶寬。Speedster7t FPGA器件中含多達8個GDDR6控制器,可支持4 Tbps的GDDR6累加帶寬,并以很小的成(chéng)本可提供與基于HBM的FPGA等效存儲帶寬。

Robert Blake表示,相較于基于HBM的FPGA,采用GDDR6的FPGA方案成(chéng)本更低、更靈活。

此外,Speedster7t FPGA還(hái)有高性能(néng)的接口端口支持極高帶寬的數據流。Speedster7t FPGA器件擁有72個高性能(néng)SerDes,速度可達1~112 GBps,并帶有前向(xiàng)糾錯(FEC)的硬件400G以太網MAC,支持4x100G和8x50G的配置,每個控制器有8或16個通道(dào)的硬件PCI Express Gen5控制器。

在安全防護方面(miàn),Speedster7t FPGA可用比特流安全保護功能(néng)應對(duì)第三方攻擊,多層防禦以可保護比特流的保密性和完整性。密鑰基于防篡改物理不可克隆技術(PUF)進(jìn)行加密,比特流由256位的AES-GCM加密算法進(jìn)行加密和驗證。

爲防止來自旁側信道(dào)的攻擊,比特流被分段,每個數據段使用單獨到處的密鑰,且解密硬件采用差分功率分析(DPA)計數器措施。此外,2084位RSA公鑰認證協議被用來激活解密和認證硬件。

今年Q4提供開(kāi)發(fā)闆

作爲FPGA芯片及FPGA IP企業,Achronix在Speedcore eFPGA IP中采用了與Speedster 7t FPGA中使用同一種(zhǒng)技術,可支持從Speedster7t FPGA到ASIC的無縫轉換。

對(duì)ASIC的轉換而言,固定功能(néng)可被固化到ASIC結構中,從而減小芯片面(miàn)積、成(chéng)本和功耗。

當使用Speedcor eFPGA IP將(jiāng)Speedster7t FPGA轉換爲ASIC,客戶有望節省50%的功耗,并降低90%的成(chéng)本。

供貨方面(miàn),Speedster7t FPGA器件的大小範圍爲從363K至2.6M的6輸入查找表(LUT),現已可提供支持所有Achronix産品的ACE設計工具,可支持包括Speedcore eFPGA和Speedchip FPGA多晶粒封裝芯片(Chipset)。

Robert Blake透露,第一批用于評估的器件和開(kāi)發(fā)闆將(jiāng)于2019年第四季度提供。